# MOBILE MULTIMEDIA INTERFACE (M<sup>2</sup>I) VERY LOW POWER 1.8V 16K X 16 SYNCHRONOUS DUAL-PORT STATIC RAM

Datasheet IDT70P9268

### **Features**

- ◆ True Dual-Ported Memory Cells

- Allows simultaneous access of the same memory location

- High per-port throughput performance

- Industrial: 800 Mbps

- **♦** Low-Power Operation

- Active: 15 mA (typ.)

- Standby: 2 uA (typ.)

- Multiplexed address and data I/Os

- Counter enable and repeat features

- Full synchronous operation on both ports

- Separate upper-byte and lower-byte controls for multiplexed bus and bus matching compatibility

- ◆ LVTTL-compatible, single 1.8V (+/- 100mV) power supply

- Industrial temperature range (-40C to +85C)

- Available in a 100-ball fpBGA (fine pitch BGA)

- ◆ Green parts available, see ordering information

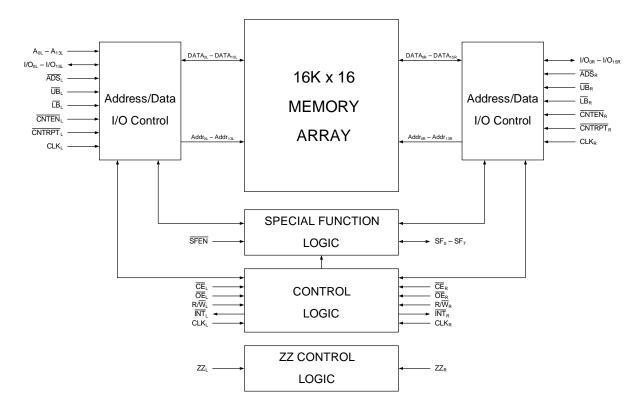

# **Block Diagram**

#### NOTES:

1. This block diagram depicts operation with the address and data signals mux'd on the right port but not on the left port. If each port is set to operate with the address and data signals mux'd, then both sides of the block diagram will be the same as the right port pictured above.

**Industrial Temperature Range**

# **Device Description**

Designed primarily for use as a high-speed, low-power inter-connect in multi-processor wireless handsets, the IDT70P9268 or Mobile Multimedia Interconnect (M<sup>2</sup>I) provides many advantages over embedded serial interfaces, asynchronous memories, and other legacy solutions to interprocessor communication.

#### **Performance**

The M<sup>2</sup>I supports unparalleled data throughput rates of up to 900 Mbps per port. This is achieved through the implementation of a synchronous architecture which allows the device to support much shorter cycle times (20 ns compared to 55 ns for most low-power asynchronous memories). Additionally, the adoption of a synchronous architecture allows the M<sup>2</sup>I to support on-chip counter functionality which helps to eliminate the inefficiencies associated with asynchronous implementations of the address-data-multiplex (ADM) interface. Asynchronous ADM (address-data multiplex) interfaces require the assertion of an external address on one cycle followed by the associated data on the subsequent cycle. This results in an access scheme that imparts a 50% inefficiency into a system already limited by slow cycle times. The M<sup>2</sup>I's counter functionality allows a single external address to be asserted on one cycle followed by data being burst into or out of the device on every subsequent cycle. This, when combined with the dramatically improved cycle time, translates to roughly six times greater throughput per-port when compared with asynchronous ADM devices.

# **Power Consumption**

In portable applications, power consumption is of vital concern. This is why the M<sup>2</sup>I includes several features targeted at reducing the power consumption of the device itself and the system as a whole. First, the M<sup>2</sup>I was designed to consume 40% less operating current than low-power asynchronous memories (15 mA compared to 25 mA). When combined with it's superior performance and counter functionality, which allow it to complete media transfers in fewer cycles, this enables the M<sup>2</sup>I to consume nearly 90% less energy than asynchronous memories during transfers of a given file size. Second, the M<sup>2</sup>I features port-specific chip-enable and sleep mode pins which allow the two ports of the M<sup>2</sup>I to be powered down into standby mode independently of one another. When combined with the M<sup>2</sup>I's interrupt flag functionality, this allows the processor subsystems to communicate with one another and to shut off whole portions of the handset which are not in use, dramatically reducing the power consumption of the system.

# Flexibility

To help meet the ever changing requirements of wireless handsets, the M²I has been designed to provide a great deal of flexibility. The M²I has the ability to support both ADM and traditional SRAM interfaces, allowing it to seamlessly interface with both current and legacy processors. Additionally, the M²I helps to free up GPIO pins on the processors, allowing designers to include differentiating functionality that helps set their product apart from the competition. By supporting the ADM interface, the M²I consumes nearly 50% fewer pins per-port than non-multiplexed solutions. The M²I also frees up additional GPIO pins on the processors by including 8 dynamically programmable GPIO extender pins. These pins allow the processors to offload the need to monitor or control simple, binary state devices (e.g. switches, LED drivers, etc.) to the M²I and allow the processors to use their GPIO pins for more value added functions.

# IDT70P9268 BY100 100-BALL fpBGA

| A1                 | A2                 | А3                 | A4    | A5      | A6                  | A7                  | A8                 | A9                  | A10                 |

|--------------------|--------------------|--------------------|-------|---------|---------------------|---------------------|--------------------|---------------------|---------------------|

| Vss                | I/O0R              | VDD                | I/O4R | I/O7R   | VDD                 | I/O10R              | VDD                | I/O15R              | SFEN                |

| B1                 | B2                 | В3                 | B4    | B5      | B6                  | B7                  | B8                 | B9                  | B10                 |

| R/W̄R              | CLKR               | I/O1R              | Vss   | I/O5R   | Vss                 | I/O11R              | Vss                | I/O14R              | ŌĒR                 |

| C1                 | C2                 | C3                 | C4    | C5      | C6                  | C7                  | C8                 | C9                  | C10                 |

| ĀDSR               | CNTENR             | CNTRPTR            | I/O2R | I/O6R   | I/O8R               | I/O12R              | ZZR                | SF7                 | Vss                 |

| D1                 | D2                 | D3                 | D4    | D5      | D6                  | D7                  | D8                 | D9                  | D10                 |

| <u>CE</u> R        | ĪNTR               | ŪBR                | ŪBR   | I/O3R   | I/O9R               | I/O13R              | SF6                | SF5                 | SF4                 |

| E1                 | E2                 | E3                 | E4    | E5      | E6                  | E7                  | E8                 | E9                  | E10                 |

| ĬNT∟               | Vss                | VDD                | ŪBL   | CNTRPTL | SF0                 | MSEL <sup>(2)</sup> | VDD                | Vss                 | VDD                 |

| F1                 | F2                 | F3                 | F4    | F5      | F6                  | F7                  | F8                 | F9                  | F10                 |

| CEL                | ĪΒL                | CNTENL             | CLKL  | Vss     | A13L <sup>(3)</sup> | SF2                 | Vss                | Vss                 | SF1                 |

| G1                 | G2                 | G3                 | G4    | G5      | G6                  | G7                  | G8                 | G9                  | G10                 |

| ĀDSL               | A0L <sup>(3)</sup> | A3L <sup>(3)</sup> | VDD   | I/O8L   | I/O12L              | A7L <sup>(3)</sup>  | ZZL                | ŌĒL                 | SF3                 |

| H1                 | H2                 | НЗ                 | H4    | H5      | H6                  | H7                  | Н8                 | H9                  | H10                 |

| R/WL               | A2L <sup>(3)</sup> | I/O0L              | Vss   | I/O4L   | I/O11L              | I/O13L              | A9L <sup>(3)</sup> | A12L <sup>(3)</sup> | NC                  |

| J1                 | J2                 | J3                 | J4    | J5      | J6                  | J7                  | J8                 | J9                  | J10                 |

| A1L <sup>(3)</sup> | A5L <sup>(3)</sup> | I/O1L              | I/O6L | I/O7L   | I/O9L               | VDD                 | I/O15L             | A10L <sup>(3)</sup> | A11L <sup>(3)</sup> |

| K1                 | K2                 | K3                 | K4    | K5      | K6                  | K7                  | K8                 | K9                  | K10                 |

| A4L <sup>(3)</sup> | A6L <sup>(3)</sup> | I/O2L              | I/O3L | I/O5L   | VDD                 | I/O10L              | Vss                | I/O14L              | A8L <sup>(3)</sup>  |

The device setup shown above features multiplexed address and data signals on the right port and non-multiplexed address and data signals on the left port.

For multiplexed address and data signal operation on the left port, this pin should be set to VDD. For non-multiplexed address and data signal operation on the left port, this pin should be set to VSS.

For multiplexed address and data signal operation on the left port, these pins should be set to VSS.

| Left Port                    | Right Port                     | Names                                       |

|------------------------------|--------------------------------|---------------------------------------------|

| ĒĒ∟                          | $\overline{CE}_R$              | Chip Enable (Input)                         |

| $R/\overline{W}_L$           | $R/\overline{W}_R$             | Read/Write Enable (Input)                   |

| ŌĒL                          | $\overline{OE}_R$              | Output Enable (Input)                       |

| $A_{0L} - A_{15L}$           | N/A                            | Address (Input)                             |

| $I/O_{0L} - I/O_{15L}$       | N/A                            | Data (Input/Output)                         |

| N/A                          | $I/O + A_{0R} - I/O + A_{15R}$ | Multiplexed Address and Data (Input/Output) |

| CLK <sub>L</sub>             | CLK <sub>R</sub>               | Clock (Input)                               |

| $\overline{U}\overline{B}_L$ | $\overline{\sf UB}_{\sf R}$    | Upper Byte Enable (Input)                   |

| $\overline{LB}_L$            | $\overline{LB}_R$              | Lower Byte Enable (Input)                   |

| ĀDSL                         | ĀŪS <sub>R</sub>               | Address Strobe Enable (Input)               |

| CNTENL                       | ŪNTĒN <sub>R</sub>             | Counter Enable (Input)                      |

| CNTRPTL                      | CNTRPT <sub>R</sub>            | Counter Repeat (Input)                      |

| ĪNĪ∟                         | ĪNT̄ <sub>R</sub>              | Interrupt Flag (Output)                     |

| $ZZ_{L}$                     | $ZZ_R$                         | Sleep Mode Enable (Input)                   |

|                              | SFEN                           | Special Function Enable (Input)             |

|                              | SF <sub>0-7</sub>              | Special Function I/O (Input/Output)         |

|                              | MSEL                           | Left Port Mode Select (Input)               |

|                              | $V_{DD}$                       | Power (1.8V)                                |

|                              | $V_{SS}$                       | Ground (0V)                                 |

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M<sup>2</sup>I) Dual Port Static RAM Industrial Truth Table I - Read/Write and Enable Control (Multiplexed Port)

| ŌĒ | CLK        | CE | ŪB | ΙB | R/W | ADS | ZZ | Upper<br>Byte    | Lower<br>Byte    | Cycle | Address        | Mode                    |  |

|----|------------|----|----|----|-----|-----|----|------------------|------------------|-------|----------------|-------------------------|--|

| Х  | <b>↑</b>   | Η  | Χ  | Х  | Х   | Х   | L  | High Z           | High Z           | Х     | Х              | Deselected              |  |

| Χ  | <b>↑</b>   | L  | Н  | Н  | Χ   | Χ   | L  | High Z           | High Z           | Х     | Х              | Both bytes deselected   |  |

| Χ  | <b>↑</b>   | L  | L  | Н  | L   | L   | L  |                  |                  | N     | $A_N$          | Write to Upper Byte     |  |

| Х  | <b>↑</b>   | Х  | Х  | Х  | L   | Н   | L  | D <sub>IN</sub>  | High Z           | N+1   |                | write to Opper Byte     |  |

| Х  | <b>↑</b>   | L  | Н  | L  | L   | L   | L  |                  |                  | N     | A <sub>N</sub> | Write to Lawer Dute     |  |

| Х  | <b>↑</b>   | Х  | Χ  | Χ  | L   | Н   | L  | High Z           | D <sub>IN</sub>  | N+1   |                | Write to Lower Byte     |  |

| Х  | <b>↑</b>   | L  | L  | L  | L   | L   | L  |                  |                  | N     | A <sub>N</sub> | Write to Both Butes     |  |

| Х  | <b>↑</b>   | Χ  | Χ  | Χ  | L   | Н   | L  | D <sub>IN</sub>  | D <sub>IN</sub>  | N+1   |                | Write to Both Bytes     |  |

| Н  | $\uparrow$ | L  | L  | Н  | Н   | L   | L  |                  |                  | N     | $A_N$          | Pood Upper Pute Only    |  |

| L  | <b>↑</b>   | Χ  | Χ  | Χ  | Н   | Н   | L  | D <sub>OUT</sub> | High Z           | N+2   |                | Read Upper Byte Only    |  |

| Н  | <b>↑</b>   | L  | Н  | L  | Н   | L   | L  |                  |                  | N     | A <sub>N</sub> | Pood Lower Pute Only    |  |

| L  | <b>↑</b>   | Χ  | Χ  | Χ  | Н   | Н   | L  | High Z           | D <sub>OUT</sub> | N+2   |                | Read Lower Byte Only    |  |

| Н  | <b>↑</b>   | L  | L  | L  | Н   | L   | L  |                  |                  | N     | A <sub>N</sub> | Pood Roth Rytos         |  |

| L  | <b>↑</b>   | Х  | Х  | Х  | Н   | Н   | L  | D <sub>OUT</sub> | D <sub>OUT</sub> | N+2   |                | Read Both Bytes         |  |

| Н  | <b>↑</b>   | L  | L  | L  | Х   | Н   | L  | High Z           | High Z           | Х     | Х              | Outputs Disabled        |  |

| Х  | Χ          | Χ  | Χ  | Χ  | Χ   | Χ   | Η  | High Z           | High Z           | Х     | Х              | Sleep Mode – Power down |  |

# **Truth Table II - Read/Write and Enable Control (Non-Multiplexed Port)**

| ŌĒ | CLK        | CE | ŪB | ĪΒ | R/W | ZZ | Upper Byte I/O   | Lower Byte I/O   | Mode                     |

|----|------------|----|----|----|-----|----|------------------|------------------|--------------------------|

| Х  | <b>↑</b>   | Н  | Χ  | Χ  | Х   | L  | High Z           | High Z           | Deselected               |

| X  | 1          | L  | Ι  | Н  | Χ   | L  | High Z           | High Z           | Both Bytes Deselected    |

| X  | $\uparrow$ | L  | L  | Η  | L   | L  | D <sub>IN</sub>  | High Z           | Write To Upper Byte Only |

| Х  | <b>↑</b>   | L  | Н  | L  | L   | L  | High Z           | D <sub>IN</sub>  | Write to Lower Byte Only |

| X  | <b>↑</b>   | L  | L  | L  | L   | L  | D <sub>IN</sub>  | D <sub>IN</sub>  | Write to Both Bytes      |

| L  | <b></b>    | L  | L  | Н  | Н   | L  | D <sub>OUT</sub> | High Z           | Read Upper Byte Only     |

| L  | <b>↑</b>   | L  | Ι  | L  | Н   | L  | High Z           | D <sub>OUT</sub> | Read Lower Byte Only     |

| L  | <b></b>    | L  | L  | L  | Н   | L  | D <sub>OUT</sub> | D <sub>OUT</sub> | Read Both Bytes          |

| Н  | 1          | L  | Ш  | L  | X   | L  | High Z           | High Z           | Outputs Disabled         |

| Х  | Χ          | Χ  | X  | Χ  | Χ   | Н  | High Z           | High Z           | Sleep Mode – Power Down  |

### **Truth Table III - Address Counter Control**

| External<br>Address | Previous<br>Internal<br>Address | Internal<br>Address<br>Used | CLK | ĀDS | CNTEN | CNTRPT | Mode                                                                  |

|---------------------|---------------------------------|-----------------------------|-----|-----|-------|--------|-----------------------------------------------------------------------|

| An                  | X                               | An                          | 1   | L   | Χ     | Н      | External Address Used                                                 |

| Х                   | An                              | A <sub>n + 1</sub>          | 1   | Н   | Ш     | Н      | Counter Enabled – Internal Address<br>Generation                      |

| Х                   | A <sub>n+1</sub>                | A <sub>n+1</sub>            | 1   | Н   | н     | Н      | External Address Blocked – Counter Disabled (A <sub>n+1</sub> reused) |

| Х                   | Х                               | A <sub>n</sub>              | 1   | Х   | Х     | L      | Counter Reset to Last External Address<br>Loaded                      |

# **Recommended Operating Temperature and Supply Voltage**

| Grade      | Ambient Temperature | GND | VDD            |

|------------|---------------------|-----|----------------|

| Industrial | -40°C to +85°C      | 0V  | 1.8V +/- 100mV |

# **Recommended DC Operating Conditions**

| Symbol | Parameter          | Min. | Тур. | Max.                  | Unit |

|--------|--------------------|------|------|-----------------------|------|

| VDD    | Supply Voltage     | 1.7  | 1.8  | 1.9                   | V    |

| Vss    | Ground             | 0    | 0    | 0                     | V    |

| VIH    | Input High Voltage | 1.2  |      | V <sub>DD</sub> + 0.2 | V    |

| VIL    | Input Low Voltage  | -0.2 |      | 0.4                   | V    |

# **Absolute Maximum Ratings**

| Symbol | Rating                                                         | Industrial         | Unit |

|--------|----------------------------------------------------------------|--------------------|------|

| VDD    | Voltage on Input, Output and I/O Terminals with Respect to Vss | -0.5V to VDD +0.3V | V    |

| VTERM  | Terminal Voltage with Respect to GND                           | -0.5V to +2.9V     | V    |

| TBIAS  | Temperature Under Bias                                         | -55 to +125        | °C   |

| Тѕтс   | Storage Temperature                                            | -65 to +150        | °C   |

| TJN    | Junction Temperature                                           | +150               | °C   |

| Іоит   | DC Output Current                                              | 20                 | mA   |

# **Capacitance**

| Symbol | Parameter          | Conditions | Max. | Unit |

|--------|--------------------|------------|------|------|

| CIN    | Input Capacitance  | VIN = 0V   | 9    | PF   |

| Соит   | Output Capacitance | VOUT = 0V  | 11   | PF   |

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (VDD = 1.8V +/- 100mV)

| Symbol | Parameter              | Test Conditions                                                           | Min.                   | Max. | Unit |

|--------|------------------------|---------------------------------------------------------------------------|------------------------|------|------|

| Iu     | Input Leakage Current  | VIN = Vss to VDD                                                          |                        | 1    | иA   |

| ILO    | Output Leakage Current | $\overline{CE}x = V_{IH} \text{ or } \overline{OE}x = V_{IH} \text{ or }$ |                        | 1    | иA   |

|        |                        | Vout = Vss to VDD                                                         |                        |      |      |

| Vol    | Output Low Voltage     | Iol = 0.1 mA, Vdd = Min                                                   |                        | 0.2  | V    |

| Vон    | Output High Voltage    | Iон = -0.1mA, V <sub>DD</sub> = Min                                       | V <sub>DD</sub> – 0.2V |      | V    |

| Volsf  | Output Low Voltage     | IoL = 4mA, VDD = Min                                                      |                        | 0.4  | V    |

# Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M<sup>2</sup>l) Dual Port Static RAM Industrial Temperature Range DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (VDD = 1.8V +/- 100mV)

| Symbol           | Parameter                                           | Test Conditions                                                                                                                                                                                                                                                | 70P          | 9268         |

|------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|

|                  |                                                     |                                                                                                                                                                                                                                                                | Тур.         | Max.         |

| ldd              | Dynamic Operating<br>Current (Both Ports<br>Active) | CEL and CER = VIL,         Outputs Disabled,         f = fMAX <sup>(1)</sup>                                                                                                                                                                                   | 15 mA        | 25 mA        |

| ISB1             | Standby Current<br>(Both Ports – TTL<br>Inputs)     | $\overline{CE}_L = \overline{CE}_R = V_{IH},$ Outputs Disabled, $f = f_{MAX}^{(1)}$                                                                                                                                                                            | 2 mA         | 4 mA         |

| I <sub>SB2</sub> | Standby Current<br>(One Port – TTL<br>Inputs)       | $\overline{CE}$ "A" = V <sub>IL</sub> and $\overline{CE}$ "B" = V <sub>IH</sub> <sup>(3)</sup> ,<br>Active Port Outputs Disabled,<br>$f = f_{MAX}^{(1)}$                                                                                                       | 3 mA         | 5 mA         |

| IsB3             | Full Standby Current<br>(Both Ports CMOS<br>Inputs) | Both Ports Outputs Disabled $\overline{CE}_L$ and $\overline{CE}_R \ge V_{DD} - 0.2V$ , $V_{IN} \ge V_{DD} - 0.2V$ , or $V_{IN} \le 0.2V$ , $f = 0^{(2)}$                                                                                                      | 2 <i>u</i> A | 8 <i>u</i> A |

| IsB4             | Full Standby Current<br>(One Port – CMOS<br>Inputs) | $\overline{\text{CE}}$ "a" $\leq 0.2 \text{V}$ and $\overline{\text{CE}}$ "b" $\geq \text{V}_{DD} - 0.2 \text{V}$ , $\text{V}_{IN} \geq \text{V}_{DD} - 0.2 \text{V}$ or $\text{V}_{IN} \leq 0.2 \text{V}$ , Active Port Outputs Disabled, $f = f_{MAX}^{(1)}$ | 3 mA         | 5 mA         |

| lzz              | Sleep Mode Current                                  | ZZL and $ZZR > VDD - 0.2V$                                                                                                                                                                                                                                     | 2 <i>u</i> A | 8 <i>u</i> A |

#### NOTES:

- 1. At f = fmax, address and control lines (except Output Enable) are cycling at the maximum frequency clock cycle of 1/tcvc, using "AC TEST CONDITIONS" at input levels of GND to 1.8V.

- 2. f = 0 means no address, clock, or control lines change. Applies only to input at CMOS level standby.

- 3. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

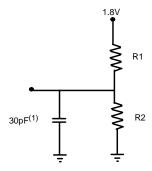

### **AC Test Conditions**

| Input Pulse Levels            | Vss to Vdd |

|-------------------------------|------------|

| Input Rise/Fall Times         | 3ns Max.   |

| Input Timing Reference Levels | VDD/2      |

| Output Reference Levels       | VDD/2      |

| Output Load                   | Figure 1   |

| 1. | 8V     |

|----|--------|

| R1 | 13500Ω |

| R2 | 13500Ω |

Figure 1. AC Output Test Level (5pF for tLz, tHz, tWz, tow)

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M<sup>2</sup>I) Dual Port Static RAM Industrial Temperature Range AC Electrical Characteristics Over the Operating Temperature Range

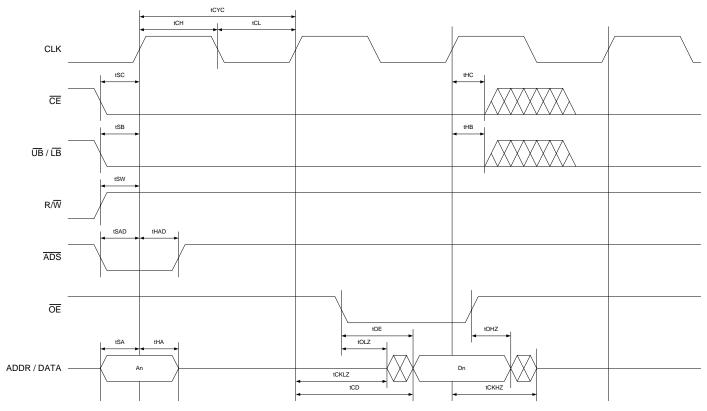

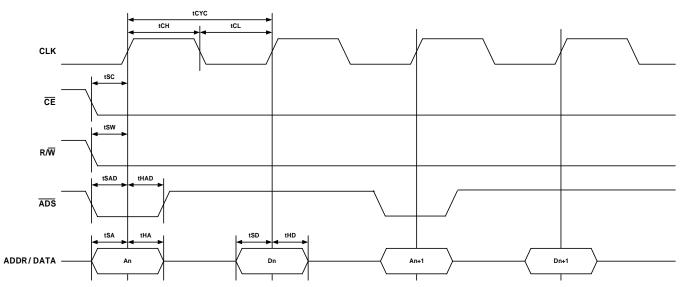

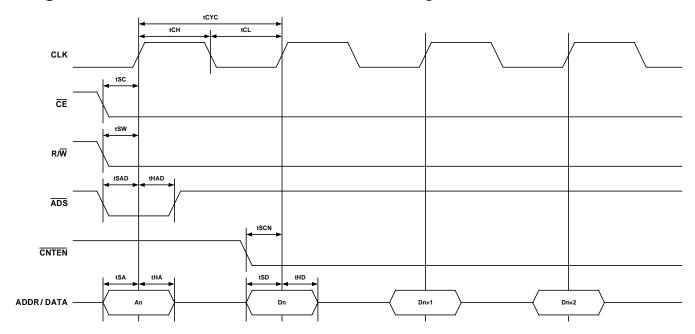

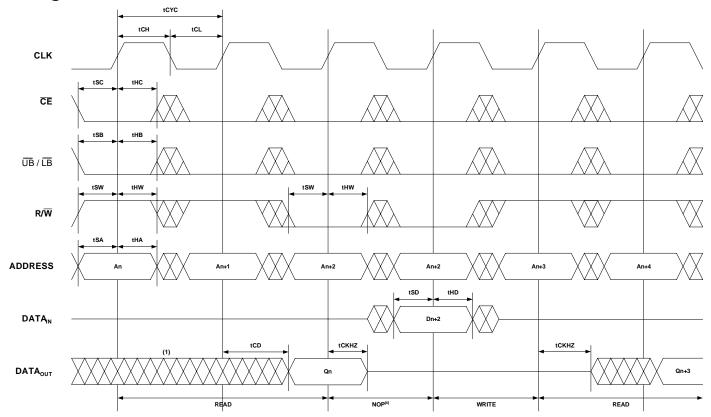

(Read and Write Cycle Timing for Multiplexed Port) (VDD = 1.8V +/- 100mV)

|                   |                                   | 70P9<br>Ind. |      |      |  |  |

|-------------------|-----------------------------------|--------------|------|------|--|--|

| Symbol            | Parameter                         | Min.         | Max. | Unit |  |  |

| t <sub>CYC</sub>  | Clock Cycle Time                  | 20           |      | ns   |  |  |

| t <sub>CH</sub>   | Clock High Time                   | 8            |      | ns   |  |  |

| t <sub>CL</sub>   | Clock Low Time                    | 8            |      | ns   |  |  |

| t <sub>R</sub>    | Clock Rise Time                   |              | 3    | ns   |  |  |

| t <sub>F</sub>    | Clock Fall Time                   |              | 3    | ns   |  |  |

| t <sub>SA</sub>   | Address Setup Time                | 5            |      | ns   |  |  |

| t <sub>HA</sub>   | Address Hold Time                 | 1            |      | ns   |  |  |

| t <sub>SB</sub>   | Bite Enable Setup Time            | 5            |      | ns   |  |  |

| t <sub>HB</sub>   | Bite Enable Hold Time             | 1            |      | ns   |  |  |

| t <sub>SC</sub>   | Chip Enable Setup Time            | 5            |      | ns   |  |  |

| t <sub>HC</sub>   | Chip Enable Hold Time             | 1            |      | ns   |  |  |

| t <sub>SW</sub>   | R/W Setup Time                    | 5            |      | ns   |  |  |

| t <sub>HW</sub>   | R/W Hold Time                     | 1            |      | ns   |  |  |

| t <sub>SD</sub>   | Input Data Setup Time             | 5            |      | ns   |  |  |

| t <sub>HD</sub>   | Input Data Hold Time              | 1            |      | ns   |  |  |

| t <sub>SAD</sub>  | ADS Setup Time                    | 5            |      | ns   |  |  |

| t <sub>HAD</sub>  | ADS Hold Time                     | 1            |      | ns   |  |  |

| t <sub>SCN</sub>  | CNTEN Setup Time                  | 5            |      | ns   |  |  |

| t <sub>HCN</sub>  | CNTEN Hold Time                   | 1            |      | ns   |  |  |

| t <sub>SRST</sub> | CNTRST Setup Time                 | 5            |      | ns   |  |  |

| t <sub>HRST</sub> | CNTRST Hold Time                  | 1            |      | ns   |  |  |

| toE               | Output Enable to Data Valid       |              | 10   | ns   |  |  |

| t <sub>OLZ</sub>  | Output Enable to Low Z            | 2            |      | ns   |  |  |

| t <sub>OHZ</sub>  | Output Enable to High Z           |              | 10   | ns   |  |  |

| t <sub>CD</sub>   | Clock to Data Valid               |              | 12   | ns   |  |  |

| t <sub>DC</sub>   | Data Output Hold After Clock High | 2            |      | ns   |  |  |

| t <sub>CKHZ</sub> | Clock High to Output High Z       | 2            | 9    | ns   |  |  |

| t <sub>CKLZ</sub> | Clock High to Output Low Z        | 2            |      | ns   |  |  |

| t <sub>INS</sub>  | Interrupt Flag Set Time           | 12           |      | ns   |  |  |

| t <sub>INR</sub>  | Interrupt Flag Reset Time 12      |              |      |      |  |  |

| t <sub>CO</sub>   | Clock to Clock Offset             | 5            |      | ns   |  |  |

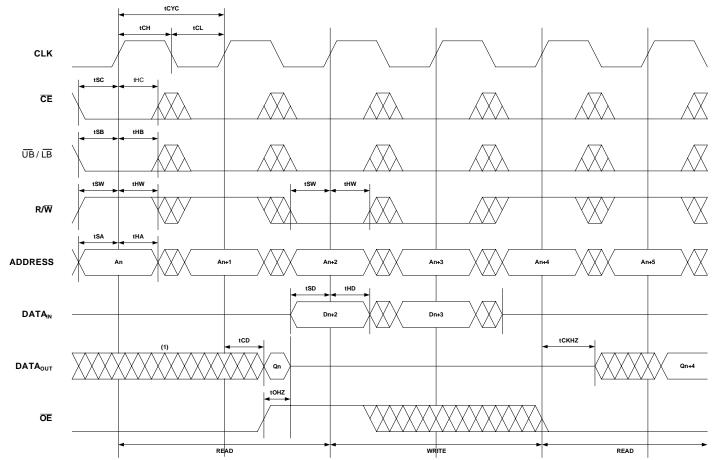

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M<sup>2</sup>I) Dual Port Static RAM Industrial Temperature Range AC Electrical Characteristics Over the Operating Temperature Range

(Read and Write Cycle Timing for Non-Multiplexed Port) (VDD = 1.8V +/- 100mV)

|                   |                                   | 70P9<br>Ind. |      |      |  |  |  |

|-------------------|-----------------------------------|--------------|------|------|--|--|--|

| Symbol            | Parameter                         | Min.         | Max. | Unit |  |  |  |

| t <sub>CYC</sub>  | Clock Cycle Time                  | 20           |      | ns   |  |  |  |

| t <sub>CH</sub>   | Clock High Time                   | 8            |      | ns   |  |  |  |

| t <sub>CL</sub>   | Clock Low Time                    | 8            |      | ns   |  |  |  |

| t <sub>R</sub>    | Clock Rise Time                   |              | 3    | ns   |  |  |  |

| t <sub>F</sub>    | Clock Fall Time                   |              | 3    | ns   |  |  |  |

| t <sub>SA</sub>   | Address Setup Time                | 5            |      | ns   |  |  |  |

| t <sub>HA</sub>   | Address Hold Time                 | 1            |      | ns   |  |  |  |

| t <sub>SB</sub>   | Bite Enable Setup Time            | 5            |      | ns   |  |  |  |

| t <sub>HB</sub>   | Bite Enable Hold Time             | 1            |      | ns   |  |  |  |

| t <sub>sc</sub>   | Chip Enable Setup Time            | 5            |      | ns   |  |  |  |

| t <sub>HC</sub>   | Chip Enable Hold Time             | 1            |      | ns   |  |  |  |

| t <sub>sw</sub>   | R/W Setup Time                    | 5            |      | ns   |  |  |  |

| t <sub>HW</sub>   | R/W Hold Time                     | 1            |      | ns   |  |  |  |

| t <sub>SD</sub>   | Input Data Setup Time             | 5            |      | ns   |  |  |  |

| t <sub>HD</sub>   | Input Data Hold Time              | 1            |      | ns   |  |  |  |

| t <sub>SAD</sub>  | ADS Setup Time                    | 5            |      | ns   |  |  |  |

| t <sub>HAD</sub>  | ADS Hold Time                     | 1            |      | ns   |  |  |  |

| t <sub>SCN</sub>  | CNTEN Setup Time                  | 5            |      | ns   |  |  |  |

| t <sub>HCN</sub>  | CNTEN Hold Time                   | 1            |      | ns   |  |  |  |

| t <sub>SRST</sub> | CNTRST Setup Time                 | 5            |      | ns   |  |  |  |

| t <sub>HRST</sub> | CNTRST Hold Time                  | 1            |      | ns   |  |  |  |

| t <sub>OE</sub>   | Output Enable to Data Valid       |              | 10   | ns   |  |  |  |

| t <sub>OLZ</sub>  | Output Enable to Low Z            | 2            |      | ns   |  |  |  |

| t <sub>OHZ</sub>  | Output Enable to High Z           |              | 10   | ns   |  |  |  |

| t <sub>CD</sub>   | Clock to Data Valid               |              | 12   | ns   |  |  |  |

| t <sub>DC</sub>   | Data Output Hold After Clock High | 2            |      | ns   |  |  |  |

| t <sub>CKHZ</sub> | Clock High to Output High Z       | 2            | 10   | ns   |  |  |  |

| t <sub>CKLZ</sub> | Clock High to Output Low Z 2      |              |      |      |  |  |  |

| t <sub>INS</sub>  | Interrupt Flag Set Time           | 12           |      | ns   |  |  |  |

| t <sub>INR</sub>  | Interrupt Flag Reset Time 12      |              |      |      |  |  |  |

| t <sub>co</sub>   | Clock to Clock Offset             | 5            |      | ns   |  |  |  |

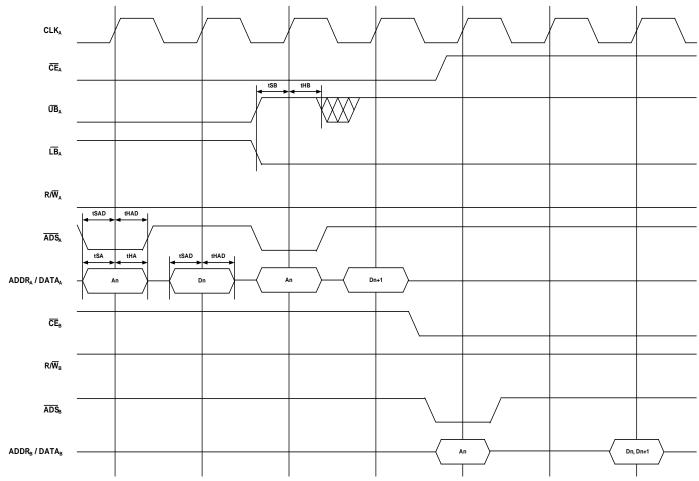

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M<sup>2</sup>I) Dual Port Static RAM Timing Waveform for Mux'd Port Single Read Cycle

# Timing Waveform for Mux'd Port Burst Read Cycle

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M<sup>2</sup>I) Dual Port Static RAM Timing Waveform for Mux'd Port Single Write Cycle

# **Timing Waveform for Mux'd Port Burst Write Cycle**

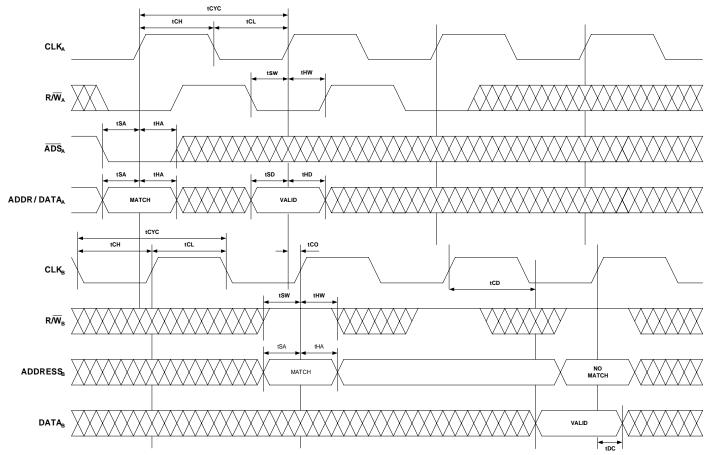

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M²I) Dual Port Static RAM Indus Timing Waveform of Mux'd Port Write to Non-Mux'd Port Read

<sup>1.</sup> CE, UB/LBn = VIL; CNTEN and CNTRPT = VIH.

2. OE = VIL for Port, which is being read from. OE = VIH for Mux'd Port, which is being written to.

3. If tco ≤ minimum specified, then data from Non-Mux'd Port read is not valid until following Non-Mux'd Port clock cycle (i.e., time from write to valid read on opposite port will be tco + 2 tcyc2 + tcp2). If tco > minimum, then data from Non-Mux'd Port read is available on first Non-Mux'd Port clock cycle (i.e., time from write to valid read on opposite port will be tco + tcyc2 + tcp2). + tcD2).

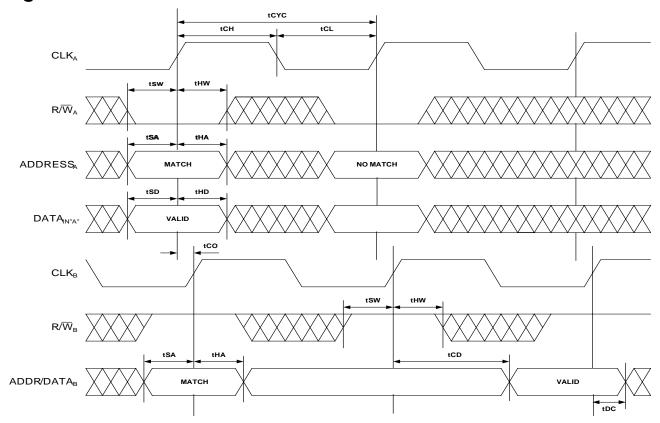

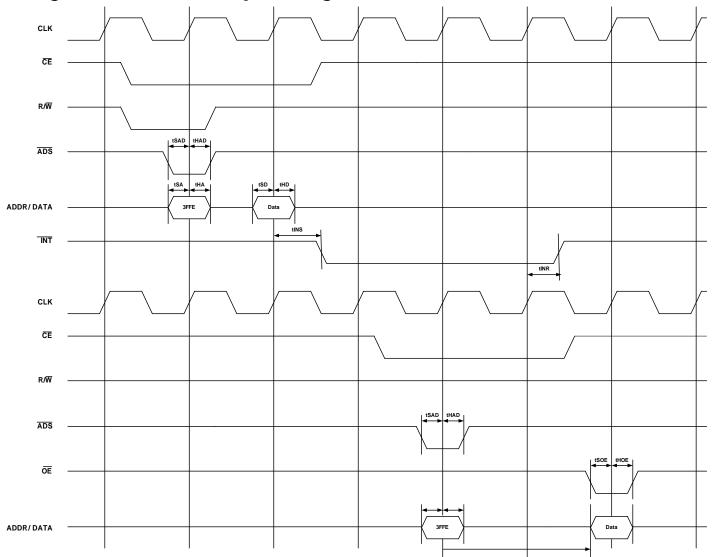

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M²I) Dual Port Static RAM Indust Timing Waveform of Non-Mux'd Port Write to Mux'd Port Read

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M<sup>2</sup>I) Dual Port Static RAM **Timing Waveform of Non-Mux'd Port Read-to-Write-to-Read**

- 1. Output state (High, Low, or High-impedance) is determined by the previous cycle control signals. 2.  $\overline{\text{CE}}$  and  $\overline{\text{ADS}} = \text{VIL}$ ;  $\overline{\text{CNTEN}}$ , and  $\overline{\text{CNTRPT}} = \text{VIH}$ . "NOP" is "No Operation".

- 3. Addresses do not have to be accessed sequentially since  $\overline{ADS}$  =  $\dot{V}IL$  constantly loads the address on the rising edge of the CLK; numbers

- are for reference use only.

4. "NOP" is "No Operation." Data in memory at the selected address may be corrupted and should be re-written to guarantee data integrity.

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M²I) Dual Port Static RAM Industrial Temperature Range Timing Waveform of Non-Mux'd Port Read-to-Write-to-Read (OE Controlled)

- 1. Output state (High, Low, or High-impedance) is determined by the previous cycle control signals. 2.  $\overline{\text{CE}}$  and  $\overline{\text{ADS}}$  = V<sub>IL</sub>;  $\overline{\text{CNTEN}}$ , and  $\overline{\text{CNTRPT}}$  = V<sub>IH</sub>. "NOP" is "NO Operation".

- 3. Addresses do not have to be accessed sequentially since  $\overline{ADS}$  = Vil. constantly loads the address on the rising edge of the CLK; numbers are for reference use only.

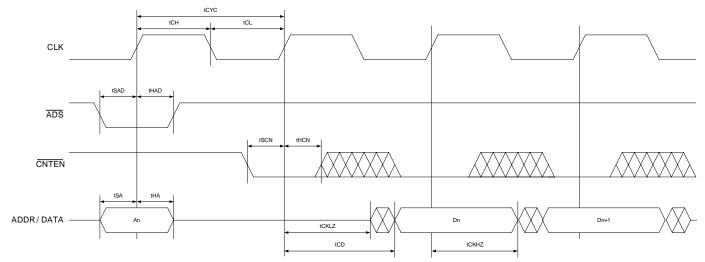

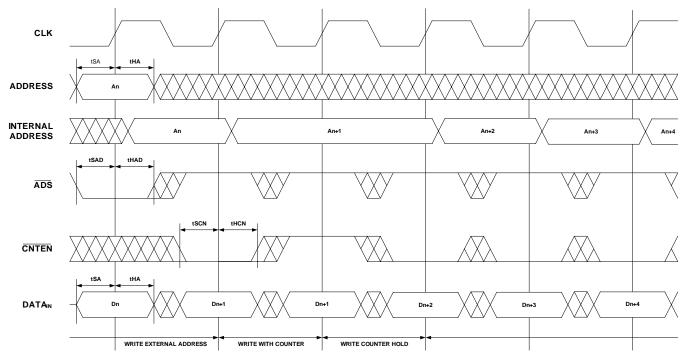

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M<sup>2</sup>I) Dual Port Static RAM Industrial To Timing Waveform of Non-Mux'd Port Write with Counter Advance

NOTES:

1. <u>CE</u>, <u>UB/LB</u>, and R/W = V<sub>IL</sub>; <u>CNTRPT</u> = V<sub>IH</sub>.

2. <u>CE</u>, <u>UB/LB</u> = V<sub>IL</sub>.

3. <u>The "Int</u>ernal Address" is equal to the "External Address" when <u>ADS</u> = V<sub>IL</sub> and equals the counter output when <u>ADS</u> = V<sub>IH</sub>.

4. <u>CNTEN</u> = V<sub>IL</sub> advances Internal Address from 'An' to 'An +1'. The transition shown indicates the time required for the counter to advance. The 'An +1'Address is written to during this

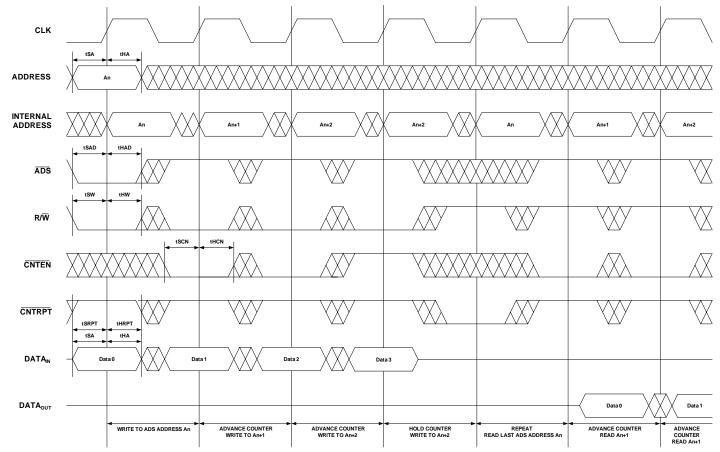

# Timing Waveform of Non-Mux'd Port Operation with Counter Repeat

- 1.  $\overline{CE}$ ,  $\overline{UB}/\overline{LB}$  = VIL.

- 2. The "Internal Address" is equal to the "External Address" when  $\overline{ADS} = VIL$  and equals the counter output when  $\overline{ADS} = VIH$ .

- 3. No dead cycle exists during CNTRPT operation. A READ or WRITE cycle may be coincidental with the counter CNTRPT cycle: Address loaded by last valid ADS load will be accessed.

4. CNTEN = VIL advances Internal Address from 'An' to 'An +1'. The transition shown indicates the time required for the counter to advance. The 'An +1'Address is written to during this

- cycle.

# IDT70P9268 Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M<sup>2</sup>I) Dual Port Static RAM Timing Waveform for x8 to x16 Bus Matching

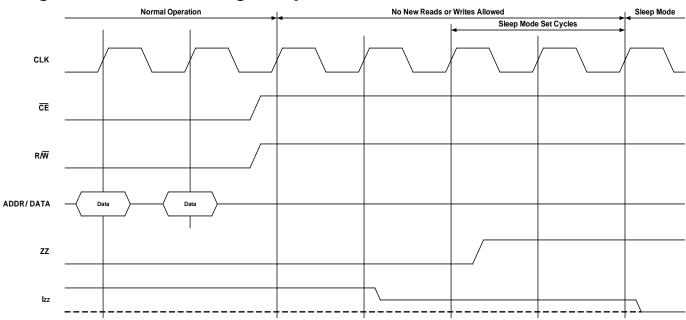

# Timing Waveform - Entering Sleep Mode

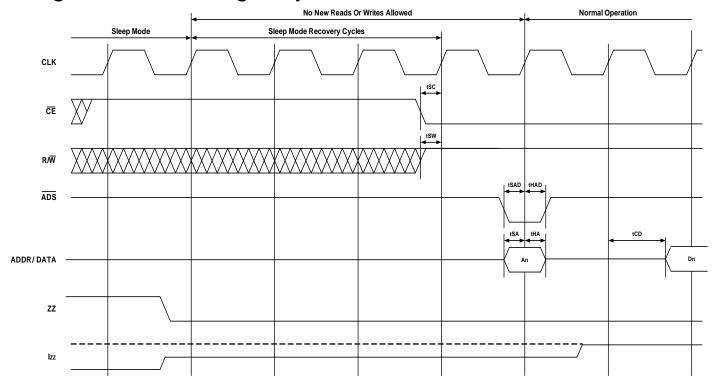

# **Timing Waveform - Exiting Sleep Mode**

# **Functional Description**

The 70P9268L provides a true synchronous multiplexed and non-multiplexed Dual-Port Static RAM interface. Registered inputs provide minimal setup and hold times on address, data, and all critical control inputs. All internal registers are clocked on the rising edge of the clock signal. Counter enable and counter repeat inputs are provided to facilitate burst reads and writes to the memory.

# **Synchronous Interrupts**

If the user chooses the interrupt function, a memory location (mail box or message center) is assigned to each port. The left port interrupt flag ( $\overline{\text{INTL}}$ ) is asserted when the right port writes to memory location 3FFE (HEX), where a write is defined as  $\overline{\text{CE}}_R = R/\overline{W}_R = \text{VIL}$ . The left port clears the interrupt through access of address location 3FFE when  $\overline{\text{CE}}_L = \text{VIL}$ ,  $R/\overline{W}_L = \text{VIH}$ . Likewise, the right port interrupt flag ( $\overline{\text{INTR}}$ ) is asserted when the left port writes to memory location 3FFF (HEX) and to clear the interrupt flag ( $\overline{\text{INTR}}$ ), the right port must read the memory location 3FFF. The message (16 bits) at 3FFE or 3FFF is user-defined since it is an addressable SRAM location. If the interrupt function is not used, address, locations 3FFE and 3FFF are not used as mail boxes, but as part of the random access memory.

# **Truth Table IV - Interrupt Flag**

| Left Port |                  |     |         |      | Right Port       |                    |                         |         |      |                       |

|-----------|------------------|-----|---------|------|------------------|--------------------|-------------------------|---------|------|-----------------------|

| CLKL      | R/₩ <sub>L</sub> | ĒΕ∟ | $ADD_L$ | ĪNŦ∟ | CLK <sub>R</sub> | $R/\overline{W}_R$ | <b>C</b> E <sub>R</sub> | $ADD_R$ | ĪÑ₹ĸ | Function              |

| <b>1</b>  | L                | L   | 3FFF    | Χ    | <b>^</b>         | Χ                  | Х                       | X       | L    | Set Right INTR Flag   |

| <b>1</b>  | Х                | Χ   | X       | Χ    | +                | Н                  | L                       | 3FFF    | Н    | Reset Right INTR Flag |

| <b>1</b>  | Х                | Χ   | X       | L    | <b>1</b>         | L                  | L                       | 3FFE    | Х    | Set Left INTL Flag    |

| <b>1</b>  | Н                | Ĺ   | 3FFE    | Н    | <b>^</b>         | X                  | Х                       | X       | X    | Reset Left INTL Flag  |

# **Advanced Input Read and Output Drive Registers**

The IDT70P9268L is equipped with 8 Special Function (SFx) pins that can be programmed to function as either Input Read Register (IRR) or Output Drive Register (ODR) pins. IRR pins allow the user to capture the status of external binary state devices and report that status to a processor, ASIC, FPGA, etc. via a standard read access from either port. ODR pins allow the user to monitor and control the state of external binary state devices via standard reads and writes from either port. The functionality of the SF pins are determined by the status of the Pin Direction Register (PDR). Refer to Truth Table V for information on programming the PDR and operating the special function pins.

# **Truth Table V - Input Read and Output Drive Registers**

| SFEN | ADDR | R/₩ | 1/00 – 1/07 | 1/08   | I/O9 – I/O15 | Function                           |

|------|------|-----|-------------|--------|--------------|------------------------------------|

| L    | 0    | L   | Note 1      | Н      | X            | Program Pin Direction Register     |

| L    | 0    | Н   | Note 2      | Note 3 | Note 3       | Reading the status of SFn and PDRn |

| L    | 0    | L   | Note 4      | L      | X            | Write to Output Drive Register     |

- 1. If I/On = H, SFn is programmed as an output and I/On will be used to read and write to this ODR location during subsequent transactions when I/O8 = L. If I/On= L, SFn is programmed as an input and I/On will be used to read this IRR location during subsequent reads where I/O8 = L.

- 2. For n = 0-7. If PDRn = 0, I/On = IRRn (the registered value of SFn). If PDRn = 1, I/On = ODRn (the value last written to ODRn).

- 3. For n = 8-15, I/On = PDRn-8.

- 4. For I/Oo I/O7, the value written to I/On will be input to each ODRn location (where PDRn = 1) with a "1" corresponding to "on" and a "0" corresponding to "off".

# **Special Function I/O Operation**

| I/O    | Function                                                                                                                                                                                                                                                                                                                                                         |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 – 7  | With $\overline{SFEN} = L$ , I/O8 = H, the value written to address 0 on I/On will determine the                                                                                                                                                                                                                                                                 |

|        | status of PDRn (1 = output, 0 = input). With $\overline{S}\overline{F}\overline{E}\overline{N}$ = L, I/O8 = L, the value written to address 0 on I/On will be input to the corresponding ODRn location (1 = on, 0 = off).                                                                                                                                        |

| 8      | With $\overline{SFEN} = L$ , writing a "0" to address 0 on this I/O causes the values of I/O <sub>0</sub> – I/O <sub>7</sub> to                                                                                                                                                                                                                                  |

|        | be input to their corresponding ODR locations. With $\overline{SFEN} = L$ , writing a "1" to address 0 on this I/O causes the values of I/O <sub>0</sub> – I/O <sub>7</sub> to be input to their corresponding PDR locations, which in turn determine whether SF <sub>0</sub> – SF <sub>7</sub> are individually programmed to be inputs (IRR) or outputs (ODR). |

| 9 – 15 | With $\overline{SFEN}$ = L, reads to address 0 will output the status of the PDR, where I/On = PDRn-8                                                                                                                                                                                                                                                            |

The PDR determines whether the SFx pins will operate as IRR or ODR. The PDR is programmed by writing to address x0000 with  $\overline{\text{SFEN}} = \text{VIL}$  and I/O8 = H. Writing a "0" to I/Ox will set SFx to be an IRR pin. Writing a "1" to I/Ox will set SFx to be an ODR pin.

The status of the Special Function pins and the PDR can be read as a standard memory access to address x0000 from either port and the data is output via the standard I/Os (Truth Table V). During Special Function reads I/O0 - I/O7 output the status of the Special Function pins with I/On corresponding to SFn. I/O8 - I/O15 outputs the status of the Pin Direction Register with I/On = PDRn-8.

For SF pins set to ODR operation, the status of these pins is determined by using standard write accesses from either port to address x0000 with SFEN = VIL and I/O8 = L. A written "1" will correspond to "on" for the connected binary state device and a written "0" will correspond to "off".

# **Sleep Mode**

The IDT70P9268 is equipped with an optional sleep or low-power mode on both ports. The sleep mode pin on both ports is asynchronous and active high. During normal operation, the ZZ-pin is pulled low. When ZZ is pulled high, the port will enter sleep mode where it will meet lowest possible power conditions. The sleep mode timing diagram shows the modes of operation: Normal Operation. No Read/Write Allowed and Sleep Mode.

For normal operation all inputs must meet setup and hold times prior to sleep and after recovering from sleep. Clocks must also meet cycle high and low times during these periods. Three cycles prior to asserting ZZ (ZZX = VIH) and three cycles after de-asserting ZZ (ZZX = VIL), the device must be disabled via the chip enable pins. If a write or a read operation occurs during these periods, the memory array may be corrupted. Validity of data out from the RAM cannot be guaranteed immediately after ZZ is asserted (prior to being in sleep). When exiting sleep mode, the device must be in Read mode ( $R/\overline{W}X = VIH$ ) when chip enable is asserted, and the chip enable must be valid for one full cycle before a read will result in the output of valid data.

During sleep mode the RAM automatically deselects itself. The RAM disconnects its internal clock buffer. The external clock may continue to run without impacting the RAMs sleep current (Izz). All outputs will remain in high-Z state while in sleep mode. All inputs are allowed to toggle. The RAM will not be selected and will not perform any reads or writes.

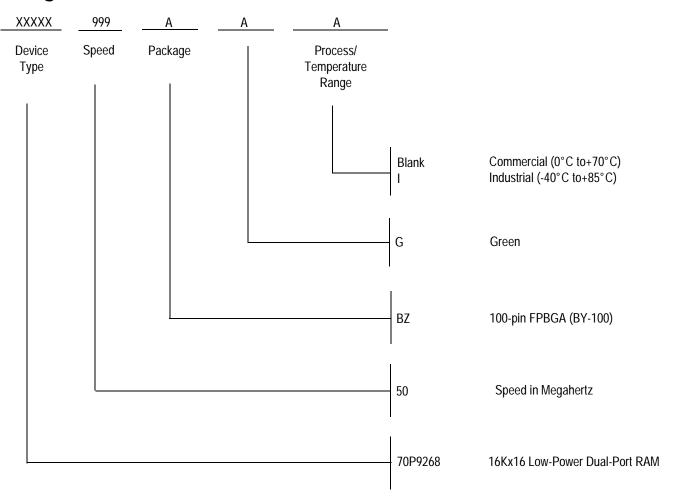

# **Ordering Information**

# **Revision History**

02/06/07: Initial Release

08/21/07: Final Datasheet. Initial Release

11/16/07: Signal corrections - added overbars to indicate low active signals. See pages 3, 4, 5, 21 & 22.

FBD correction - changed signal arrow indicator for Addrol - Addrol and added overbar to SFEN to indicate low active signal. See page 1.

Footnote correction - removed CE1 and replaced REPEAT with CNTRPT. See pages 12, 14, 15 & 16.

Footnote correction - removed  $\overline{\mathsf{UB}}/\overline{\mathsf{LB}}$ . See pages 14 & 15.

Unit measurement column corrected for DC Electrical Chars Over Operating Temp & Supply Voltage Range table. See page 6.

Added Bite Enable Setup Time (tsb), Bite Enable Hold Time (thb) values and the unit measurement column to the AC Electrical Chars Over Operating Temp Range tables. See pages 8 & 9.

Added Output Enable to Data Valid (toE) values to the AC Electrical Chars Over Operating Temp Range table (non-multiplexed port). See page 9.

Corrected the Clock High to Output Low Z (tcklz) symbol in the Timing Waveform for Mux'd Port Single Read Cycle. See page 10.

CORPORATE HEADQUARTERS

6024 Silver Creek Valley Road San Jose, CA 95138 for SALES:

800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com

for Tech Support: 408-284-2794 DualPortHelp@idt.com